## ABCs of ADCs

**Analog-to-Digital Converter Basics**

#### **Nicholas Gray**

**Data Conversion Systems Staff Applications Engineer**

November 24, 2003

### Agenda - ABCs of ADCs

- What's an ADC?

- Review of Definitions

- Sources of Distortion and Noise

- Common Design Mistakes

- High Speed ADCs at National

2

Here is a capsule of what we will discuss today. Much of this will be a review for many of you, but everyone should find some new information here.

#### What Is an ADC?

- Mixed-Signal Device

- Analog Input

- Digital Output

- Is a Divider

- Output: Input is What Fraction of V<sub>REF</sub>?

- Output =  $2^n \times G \times A_{IN} / V_{REF}$

- n = # of Output Bits (Resolution)

- G = Gain Factor (usually "1")

- A<sub>IN</sub> = Analog Input Voltage (or Current)

- V<sub>REF</sub> = Reference Voltage (or Current)

3

Because the Analog-to-Digital Converter (A/D Converter or ADC) has both analog and digital functions, it is a mixed-signal device. Many of us consider the ADC to be a mysterious device. It can, however, be considered very simply to be the instrument that it is: a device that provides an output that digitally represents the input voltage or current level.

Notice I said **voltage** or **current**. Most ADCs convert an input voltage to a digital word, but the true definition of an ADC does include the possibility of an input current.

An ADC has an analog **reference** voltage or current against which the analog input is compared. The digital output word tells us what fraction of the reference voltage or current is the input voltage or current. So, basically, the ADC is a divider.

The Input/Output transfer function is given by the formula indicated here. If you have seen this formula before, you probably did not see the "G" term (gain factor). This is because we generally consider this to be unity. However, National Semiconductor has introduced a ADCs with a gain other factors, so it is important to understand that this factor is present.

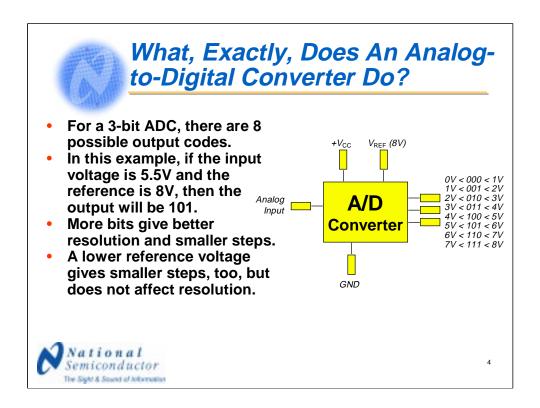

Here is an example of a 3-bit A/D converter. Because it has 3 bits, there are  $2^3 = 8$  possible output codes. The difference between each output code if  $V_{REF} / 2^3$ .

Assuming that the output response has no errors, every time you increase the voltage at the input by 1 Volt, the output code will increase by one bit. This means, in this example, that the least significant bit (LSB) represents 1 Volt, which is the smallest increment that this converter can resolve.

Note that if you reduce the reference voltage to 0.8V, the LSB would then represent 100mV, allowing you to measure a smaller range of voltages (0 to 0.8V) with greater accuracy. This is a common way for our customers to get better precision from a converter without buying a more expensive, higher resolution converter.

The Resolution of an A/D converter is the number of output bits it has.

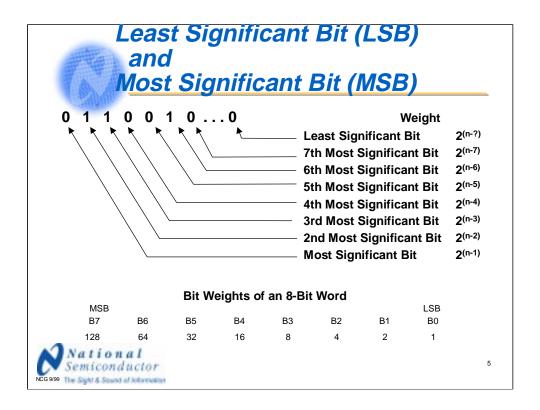

The Least and Most Significant Bits (LSB and MSB) are just what their name implies: those bits that have the least (LSB) and (MSB) weight in a digital word. For an n-bit word, the MSB has a weight of  $2^{(n-1)}$ , where "n" is the total number of bits in the word. The LSB has a weight of 1.

Dynamic Range is the ratio of the largest to the smallest possible signals that can be resolved.

| Resolution (Bits) | Dynamic Range (dB) |

|-------------------|--------------------|

| 6                 | 36.0               |

| 8                 | 48.1               |

| 10                | 60.2               |

| 12                | 72.2               |

| 14                | 84.3               |

| 16                | 96.3               |

| 18                | 108.4              |

| 20                | 120.4              |

Dynamic Range =  $20 * Log(2^n - 1)$

ь

Dynamic range is the ratio of the largest to the smallest signal that can be resolved. The largest output code, of course, is  $2^n$  -1 and the smallest signal is 1. Dynamic range in dB, then, is

$$20 * Log((2^{n}-1)/1) = 20 * Log(2^{n}-1).$$

# LSB Values by Resolution and Reference Voltage

The value of an LSB depends upon the ADC Reference Voltage and Resolution

| $V_{REF}$ | Resolution | 1 LSB     |

|-----------|------------|-----------|

| 1.00V     | 8          | 3.9062 mV |

| 1.00V     | 12         | 244.14 μV |

| 2.00V     | 8          | 7.8125 mV |

| 2.00V     | 10         | 1.9531 mV |

| 2.00V     | 12         | 488.28 μV |

| 2.048V    | 10         | 2.0000 mV |

| 2.048V    | 12         | 500.00 μV |

| 4.00V     | 8          | 15.625 mV |

| 4.00V     | 10         | 3.9062 mV |

| 4.00V     | 12         | 976.56 μV |

7

Since one LSB is equal to  $V_{REF}$  /  $2^n$ , it stands to reason that better accuracy (lower error) can be realized if we did either (or both) of two things: (1) use a higher resolution converter and/or (2) use a smaller reference voltage.

The problem with higher resolution (more bits) is the cost. Also, the smaller LSB means it is difficult to find a really small signal as it becomes lost in the noise, reducing SNR performance of the converter.

The problem with reducing the reference voltage is a loss of input dynamic range. Again, we also can lose a small signal in the noise, causing a loss of SNR performance.

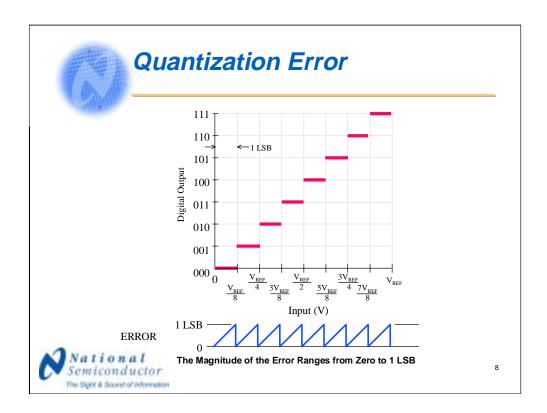

This is a simple case of a 3-bit ADC. With an ADC input of zero, the output code is zero (000). As the input voltage increases towards  $V_{REF}/8$ , the error also increases because the input is no longer zero, but the output code remains at zero because a *range* of input voltages is represented by a single output code. When the input reaches  $V_{REF}/8$ , the output code changes from 000 to 001, where the output exactly represents the input voltage and the error reduces to zero. As the input voltage increases past  $V_{REF}/8$ , the error again increases until the input voltage reaches  $V_{REF}/4$ , where the error again drops to zero. This process continues through the entire input range.

The maximum error we have here is 1 LSB. This 0 to 1 LSB range is known as the "quantization uncertainty" because there are a range of analog input values that could have caused any given code and we are uncertain at to exactly what that input voltage was. Quantization uncertainty is also known as "quantization error". This error results from the finite resolution of the ADC. That is, the ADC can only resolve the input into  $2^n$  discrete values. The converter resolution, then, is  $2^n$ . So, for an 8 Volt reference (with a unity gain factor), a 3-bit converter resolves the input into  $V_{REF}/8 = 8V/8 = 1$  Volt steps. Quantization error then is a round off error.

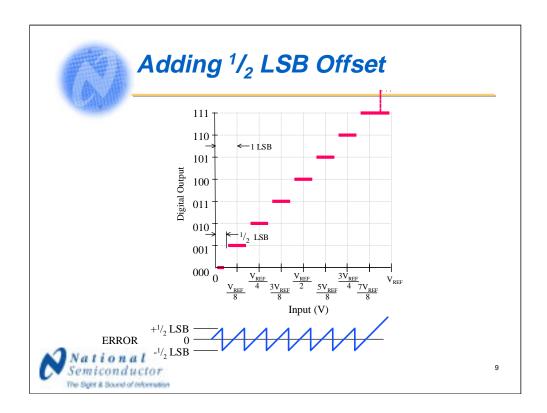

But an error of 0 to 1 LSB is not as desirable as is an error of  $\pm \frac{1}{2}$  LSB, so we introduce an offset into the A/D converter to force an error range of  $\pm \frac{1}{2}$  LSB.

If we add  $^{1}/_{2}$  LSB offset to the ADC input, the output code will change  $^{1}/_{2}$  LSB before it otherwise would. The output changes from 000 to 001 with an input value of  $^{1}/_{2}$  LSB rather than 1 LSB and all subsequent codes change at a point  $^{1}/_{2}$  LSB below where they would have changed without the offset.

With an input voltage of zero, the output code is zero (000), as before. As the input voltage increases towards the  $^{1}/_{2}$  LSB level, the error increases because the input is no longer zero, but the output code remains at zero. When the input reaches  $^{1}/_{2}$  LSB, the output code changes from 000 to 001. The input is not yet at the 1 LSB level, but only at  $^{1}/_{2}$  LSB, so the error is now  $^{-1}/_{2}$  LSB. As the input increases past  $^{1}/_{2}$  LSB, the error becomes less negative, until the input reaches 1 LSB, where the error is zero. As the input increases beyond 1 LSB, the error increases until the input reaches  $^{11}/_{2}$  LSB, where output code is increased by one and the sign of the error again becomes negative. This process continues through the entire input range.

Note that the each code transition point decreased by  $^{1}/_{2}$  LSB compared with the no offset previous page, so that the first code transition (from 000 to 001) is at  $^{+1}/_{2}$  LSB and the last code transition (from 110 to 111) is at  $^{11}/_{2}$  LSB below  $V_{REF}$ . The output of the ADC should **NOT** "rotate" with an over range input as would a digital counter that is given more clock cycles than enough to cause a full count.

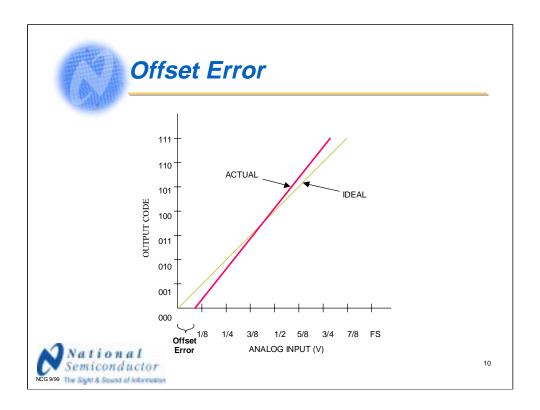

In an ideal A/D converter, an input voltage of q will just barely cause an output code transition from zero to a count of one. Any deviation from this is called Zero Scale Offset Error, Zero Scale Offset, or Offset Error, or just Offset. Offset Error is positive or negative when the first transition point is higher or lower than ideal, respectively. Offset error is a constant and can easily be factored or calibrated out. Offset error may be expressed in percent of full scale voltage or in LSB.

<u>Bottom Offset</u> differs from Offset Error in that it is the difference between the input voltage that just causes the output code to transition to the first code and the negative reference voltage (which is usually analog ground for products without a negative reference pin). It is defined as:

$$E_{OB} = V_{ZT} - V_{RB}$$

where  $\mathsf{E}_\mathsf{OB}$  is the Bottom Offset

V<sub>ZT</sub> is the first code transition input voltage

V<sub>RB</sub> is the lower reference voltage

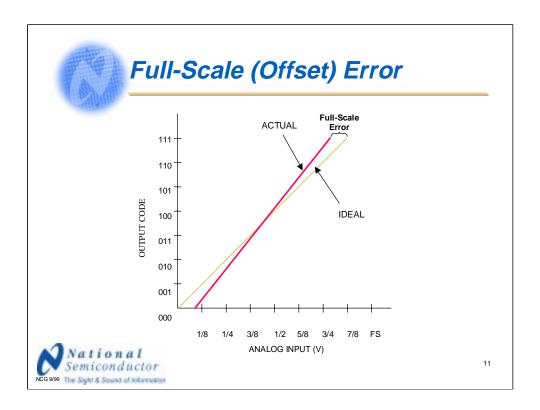

In an ideal A/D converter, the output code transition to full scale just barely occurs when the input voltage equals  $V_{REF}^*$  ( $2^n$  - 1.5) /  $2^n$ . In a real ADC the full-scale analog input causing this transition may differ somewhat from this ideal value. Part of the error will be due to offset voltage and the rest will be due to an error in the slope of the transfer function. Full Scale Error is the error in the full-scale output transition point.

The term "full-scale" can be a bit confusing at times. Full Scale Error is the difference between the input voltage that should ideally produce a full scale output code (1.5 LSB below  $V_{REF}$ ) and the actual input voltage that produces that code transition. Full Scale Error is may be expressed in LSBs or as a percentage of the full-scale voltage.

Full Scale Error is sometimes called Full Scale Offset Error.

Top Offset is yet another type of full scale error, defined as the difference between the positive reference voltage and the input voltage that just causes the output code to transition to full scale:

$$E_{OT} = V_{FT} - V_{REF}$$

.

where  $E_{\text{OT}}$  is the Top Offset voltage  $E_{\text{FT}}$  is the input voltage causing the full-scale transition  $V_{\text{RFF}}$  is the ADC reference voltage.

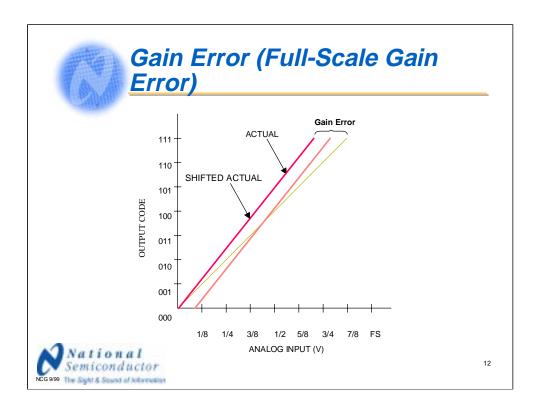

Gain Error, or Full-Scale Gain Error, is a deviation from the ideal slope of the transfer function. It is the same as full-scale error with the offset error subtracted. If we shift the actual transfer curve so that zero scale offset becomes zero, the difference between the actual and ideal transitions to full scale is the Gain Error.

Full Scale Error is expressed in LSBs, or as a percentage of the full-scale voltage.

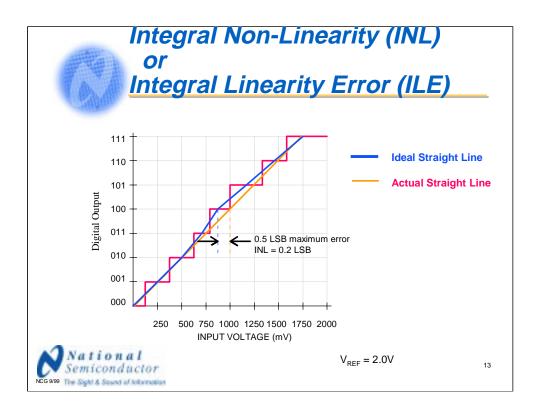

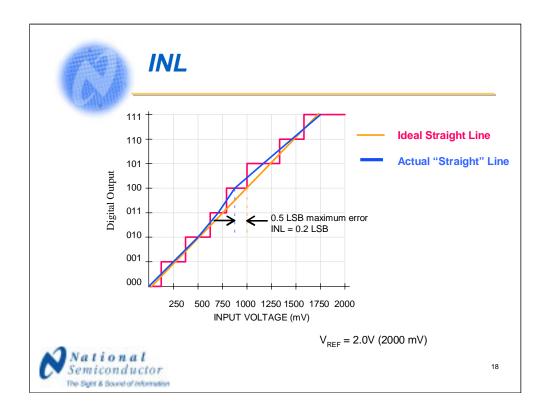

Integral Non-linearity, INL, (also called Integral Linearity Error or ILE and Linearity Error or LE) describes the departure from an ideal linear transfer curve for an ADC (or a DAC). INL does not include quantization errors, offset error, or gain error. It is a measure of the straightness of the transfer function.

The integral non-linearity of a converter can be greater than the differential non-linearity. The size and distribution of the differential errors will determine the integral linearity of the converter.

Sometimes a converter is described as being "x bits linear." For example, a converter with 10-bit resolution and 4 LSB non-linearity is sometimes described as an "8-bit linear" converter because 4 LSBs for a 10-bit device is the same as 1 LSB for an 8-bit device.

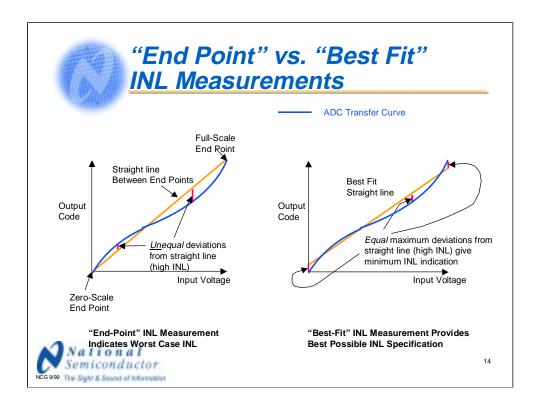

There are two methods of measuring Integral Non-Linearity (INL):

"Best-Fit" and "End Point". The Best-Fit measurement allows the supplier to show better INL specifications than does the End-Point INL measurement method. The argument for the Best-Fit method is that the customer can adjust his circuit to actually realize this low INL, achieving better overall performance. The problem doing this, however, is that each board must be adjusted for minimum INL for each individual converter, which is time-consuming and, therefore, expensive and not considered desirable or practical by most manufacturers.

The End-Point method tells the user what worst case INL he can expect if he simply makes adjustments to his two end points. Hence, the End-Point method is seen as more practical by many. Comparing INL of two competing devices is not reasonable when one is measured using the end-point method and the other uses the best-fit method as there is no correlation between the two methods. National Semiconductor uses the End-Point method.

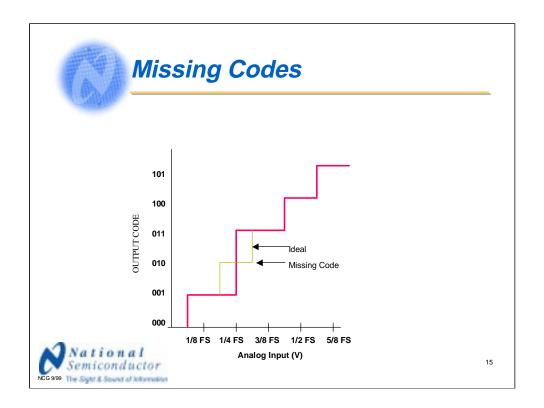

A missing code is one that no value of input voltage will produce that code at the ADC output; the code is missing from the transfer function. The transfer function above is for a three-bit A/D converter. The first code transition, from 000 to 001, takes place when the input voltage is  $^{1}/_{2}$  LSB, which is correct for an A/D converter. The second transition takes place when the input voltage reaches  $^{1}/_{4}$  FS, so the differential linearity error at that point is  $+^{1}/_{2}$  LSB. The second transition has a differential linearity error of 1 LSB, causing the output code to jump from 001 to 011, and 010 is a Missing Code.

Any time DNL exceeds the limits of

there is a possibility of one or more missing codes.

Many A/D converter data sheets specify "no missing codes" as this specification can be critical in some applications, such as servo systems.

- DNL Differential Non-Linearity

- DLE Differential Linearity Error

- INL Integral Non-Linearity

- ILE Integral Linearity Error

DNL and DLE are the same thing and describe the error in step size. This is "small scale" code to code errors.

INL and ILE are the same thing and describe the bow in the transfer function. This is "large scale" overall transfer function error.

16

Semiconductor

The Signs & Sound of Orlomation

DNL and DLE are different terms used to describe the error in step size. Similarly, INL and ILE are different terms used to describe the maximum deviation from the ideal transfer function.

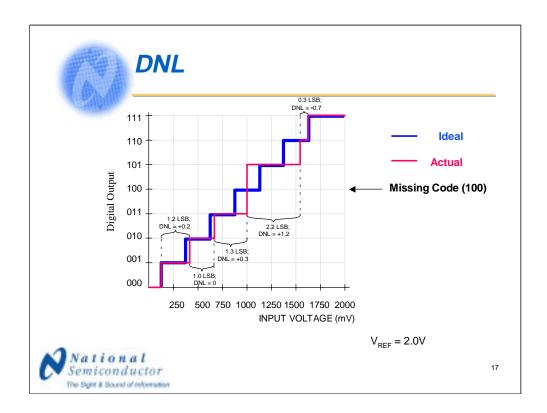

The key to remembering the difference between these two specifications is the word "Differential". DNL is the *difference* between the ideal and the actual input code width. The input code width is the range of input values that produces the same digital output code. For positive DNL we look at the widest input code range. For negative DNL we look at the narrowest code range.

INL is the maximum deviation of the transfer function from a straight line between the points defined by the first and last code transitions.

In an ideal converter, the code-to-code transition points are exactly 1 LSB apart. In an 8-bit ADC, for example, these changes are separated from each other by 1 LSB, or  $^{1}/_{256}$  of full-scale. The difference between the ideal 1 LSB and the worst case actual input voltage change between output code transitions is called Differential Non-Linearity.

DNL can be illustrated using the transfer function of a three-bit DAC shown above. Each input step should be precisely  $^{1}\!/_{8}$  of full-scale. In the example above, the first code transition (from 000 to 001) is caused by an input change of FS / 8 (250mV for the 2 Volt reference example shown here), where FS is the full-scale input. This is exactly as it should be. The second transition, from 001 to 010, has an input change that is 1.2 LSB, so is too large by 0.2 LSB. The input change for the third transition is exactly the right size. The digital output remains constant when the input voltage changes from 1000mV to beyond 1500mV and the code 101 can never appears at the output. It is **missing**. To avoid missing codes in the transfer function, DNL should be greater (more positive) than -1.0 LSB.

DNL indicates the deviation from the ideal 1 LSB step size of the analog input signal corresponding to a code-to-code increment. DNL, a static specification, relates to SNR, a dynamic specification. However, noise performance can not be predicted from DNL performance, except to say that SNR tends to become worse as DNL departs from zero.

Integral Non-Linearity, INL, describes the departure from the ideal linear transfer curve for an ADC. It is a measure of the straightness of the transfer function. The size and distribution of the differential errors will determine the integral linearity of the converter. The integral non-linearity of a converter can be greater than the differential non-linearity.

Sometimes a converter is described as being "x bits linear." For example, a converter with 10-bit resolution and 4 LSB non-linearity is sometimes described as an "8-bit linear" converter because 4 LSBs for a 10-bit device is the same as 1 LSB for an 8-bit device.

INL is a static specification and relates to THD (a dynamic specification). However, distortion performance can not be predicted from INL performance, except to say that THD tends to become worse as INL departs from zero.

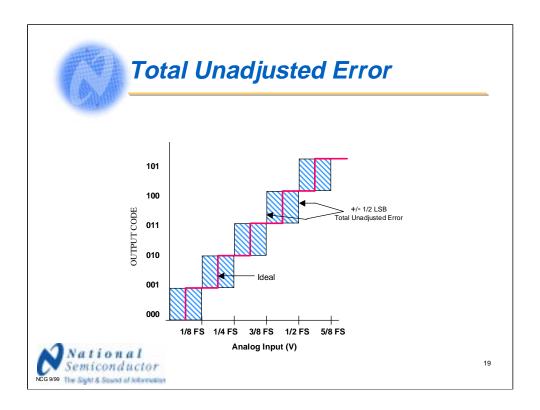

Although gain and offset errors can be trimmed externally, trimming increases costs and sometimes reduces reliability. When a designer wishes to meet a specific error budget, it is desirable to have a single specification that places a limit on errors from all sources. If this overall error limit is acceptable, no adjustments need to be made during manufacture of the end product. Total Unadjusted Error is a comprehensive specification that includes linearity errors, gain error, and offset. It is the worst-case deviation from the ideal device performance.

You won't find this specification on all of our products; it is of value only when the total error specification is less than one or two LSB, so it is generally not found on data sheets of converters with higher resolution than eight-bits. The ADC0832, for example, is specified at  $\pm^1/_2$  LSB Total Unadjusted Error. If the total unadjusted error is much larger than any one of the other error specifications, it makes sense to include separate data sheet limits for each of the errors. Otherwise, a device with  $\pm^1/_2$  LSB linearity and  $\pm 3$  LSB full-scale error might be classified simply as a "3 LSB" part and the user wouldn't know that the device could provide excellent performance in applications that require linearity but don't need full-scale accuracy.

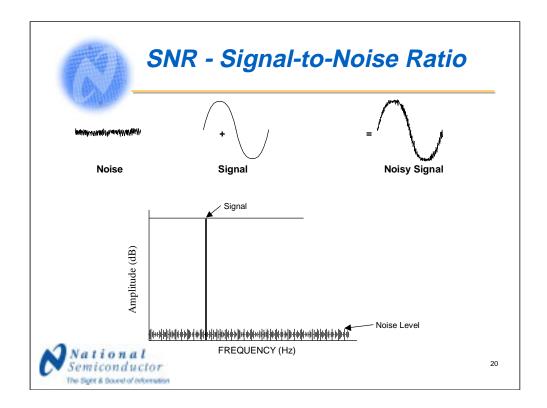

Signal-to-Noise Ratio (SNR) is the ratio of the output signal amplitude to the output noise level, not including harmonics or dc. A signal level of  $1V_{RMS}$  and a noise level of  $100\mu V_{RMS}$  yields an SNR of  $10^4$  or 80dB.

Noise level is integrated over half the clock frequency.

SNR usually degrades as frequency increases because the accuracy of the comparator(s) within the ADC degrades at higher input slew rates. This loss of accuracy shows up as noise at the ADC output.

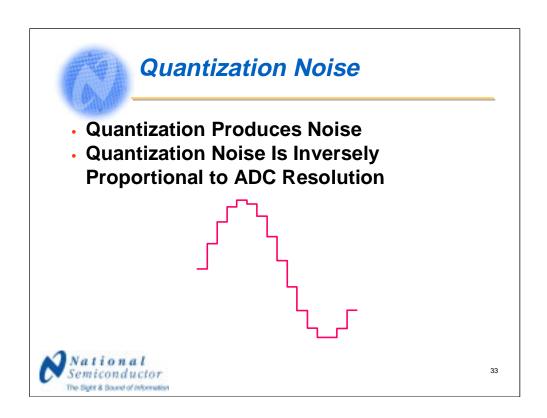

In an A/D converter, noise comes from three sources: (1) quantization noise, (2) noise generated by the converter itself and (3) application circuit noise. Quantization noise results from the quantization process--the process of assigning output codes to input ranges. Recall our discussion on quantization error. The amplitude of the quantization noise decreases as resolution increases because the size of an LSB is smaller at higher resolutions. The theoretical maximum signal-to-noise ratio for an ADC with a full-scale sine-wave input derives from quantization noise and is defined as  $20 \cdot \log(2^{(n-1)} \cdot \operatorname{sqrt}(6))$ , or about 6.02n + 1.76dB.

Application circuit noise is that noise seen by the converter as a result of the way the circuit is designed and laid out.

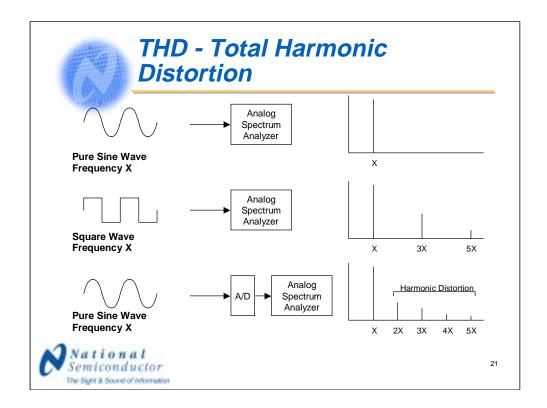

THD gives an indication of a circuit's linearity in terms of its effect on the harmonic content of a signal. An ideal, spectrally-pure sine wave has one frequency component. A complex signal such as music or speech has multiple frequency components. A square wave contains odd harmonics with specific amplitude and phase relationships. Ideally, a signal processing system will not add or subtract any harmonic components (unless that is the intended function of the signal processor). Non-linearities in a converter's transfer function, however, will produce harmonics that were not present in the original signal. Asymmetrical non-linearities will produce harmonics at even multiples of the input frequency, while symmetrical non-linearities will produce harmonics at odd multiples of the input frequency.

THD is the ratio of the rms total of the first six harmonic components to the RMS value of the output signal and relates the RMS sum of the amplitudes of the harmonics to the amplitude of the fundamental:

THD =

$$\sqrt{\frac{V_{f2}^2 + V_{f3}^2 + \dots + V_{f7}^2}{V_{f1}^2}}$$

where  $V_{f1}$  is the fundamental amplitude,  $V_{f2}$  is the second harmonic amplitude, etc.

THD can be expressed as a percentage or in dB.

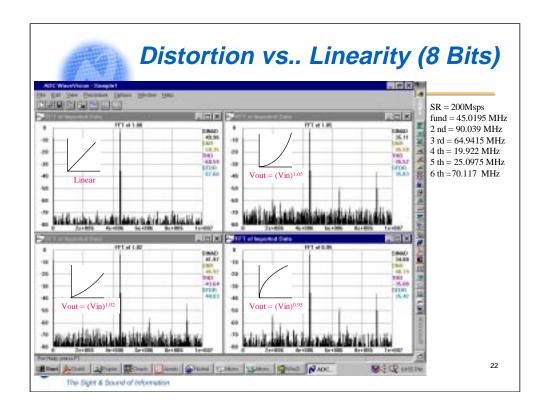

These FFT plots from our WaveVision™ software shows the distortion that results with different amounts and types of non-linearity.

The top left plot shows the results with a linear transfer function. All dynamic parameters are maximized.

The lower left plot is the result of an input to output transfer function of

Output =

$$Input^{1.02}$$

The top right plot is the result of an input to output transfer function of

Output = Input

$$^{1.05}$$

The bottom right plot results from an input to output transfer function of

Output =

$$Input^{0.95}$$

At the right of the screen capture you see the harmonic frequencies. The output frequency can never be higher than  $^{1}/_{2}$  the sample rate because of aliasing. Note how the harmonic amplitude increases as the exponent in the input to output transfer function departs from unity.

SINAD = 20 \* Log

$$\sqrt{10^{\frac{-\text{SNR}}{10}} + 10^{\frac{\text{THD}}{10}}}$$

SINAD = 10 \* Log

$$\frac{1}{10^{\frac{-SNR}{10}} + 10^{\frac{THD}{10}}}$$

23

Signal-to-Noise And Distortion (SINAD or SNDR), or Signal-to-Noise Plus Distortion (S/N+D), s a combination of the SNR and the THD specifications. It is defined as the RMS value of the output signal to the RMS value of all of the other spectral components below half the clock frequency, including harmonics but excluding dc, and can be calculated from SNR and THD according to either of the the formula here. Because it compares all undesired frequency components with the input frequency, it is an overall measure of ADC dynamic performance.

ENOB says that the ADC is equivalent to this (ENOB) number of bits as far as SINAD is concerned. That is, a converter with an ENOB of 7.0 has the same SINAD as a theoretically perfect 7-bit converter.

$$ENOB = \frac{SINAD - 1.76}{6.02}$$

24

Effective Bits (also called Effective Number Of Bits, or ENOB) is a specification that helps to quantify dynamic performance. ENOB says that the converter performs as it it were a theoretically perfect converter with a resolution of ENOB. That is, an ENOB of 7.5 bits says that converter performs, as far as SINAD is concerned, as if it were an ideal 7.5-Bit ADC.

The ideal (perfect) ADC has absolutely no distortion and the only noise it exhibits is quantization noise, so SNR then equals SINAD. Since we know that SINAD for an ideal A/D converter is (6.02n + 1.76)dB, we can substitute "ENOB" for "n" and calculate:

where SINAD is expressed in dB.

So, the number of effective bits is another method of specifying SINAD. It says that the converter is equivalent to a perfect ADC of this (ENOB) number of bits.

ENOB degrades as frequency increases for the same reason that THD degrades with frequency increase. Remember, ENOB comes from SINAD, which comes from THD and SNR.

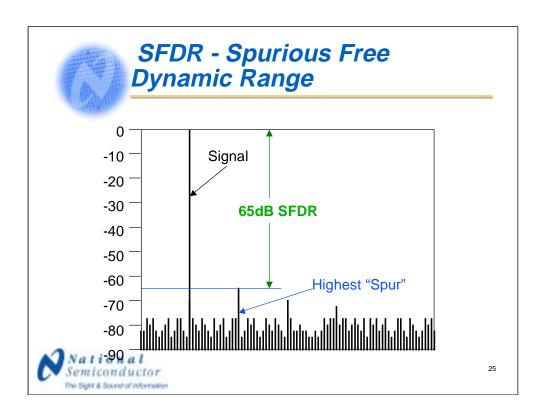

Spurious Free Dynamic Range (SFDR) is the difference between the RMS value of the desired output signal and the highest amplitude output frequency that is not present in the input, expressed in dB. Neither THD nor SINAD can ever be better than SFDR.

Some ADC suppliers ignore harmonics when specifying SFDR, but this practice is valid only if those harmonics were present at the ADC input.

Because SFDR is expressed in dB <u>below</u> the fundamental, it is sometimes expressed in negative dB. However, since it is a *range*, it should be expressed in positive dB.

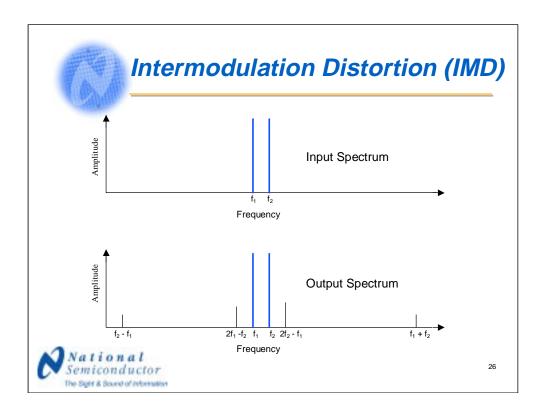

Any complex signal contains components at several frequencies simultaneously. Non-linearity in the converter's transfer function will not only cause distortion of a pure tone; it will also cause two or more signal frequencies to interact and produce intermodulation products. When this happens, the result is called intermodulation distortion, IMD.

Intermodulation distortion is normally measured with two input signals at different, closely spaced frequencies. Ideally, input frequencies  $f_1$  and  $f_2$  should produce only output frequencies of  $f_1$  and  $f_2$ . Device non-linearities, however, cause the production of new frequencies at the sum and difference frequencies of the input signals and their harmonics. i.e.  $(f_1 + f_2)$ ,  $(f_2 - f_1)$ ,  $(f_1 + 2f_2)$ ,  $(2f_1 + f_2)$ ,  $(2f_1 - f_2)$ , and  $(2f_2 - f_1)$ , etc. IMD can be expressed as the ratio of the power in the intermodulation products to the power in one of the original the input frequencies. Some applications, particularly those concerned with RF signal processing, are more sensitive to some modulation products than to others. For example, in RF applications the third-order difference products  $(2f_1 - f_2)$  and  $2f_2 - f_1)$  are important because they are closest to the input frequencies, where other terms can be digitally filtered out. For this reason the other terms are usually ignored where IMD is specified for RF applications.

## **Sources of Noise** and Distortion

# Common Sources of Noise and Distortion

- Inadequate Supply Bypassing

- Inadequate V<sub>A</sub> V<sub>DR</sub>\* Supply Decoupling

- Noisy Components/Conditioning Circuitry

- Quantization

- Clock

- Output to Input Coupling

\*  $V_{DR}$  (or DR  $V_{D}$ ) is the supply for the output drivers

28

There are many sources of signal degradation in any analog signal chain and the circuitry associated with an ADC has its share. Most of the problem areas mentioned here are common to any analog circuitry.

### Inadequate Supply Bypassing

- Noise Can Enter Via The Power Supply

- Specified PSRR Is A D.C. Measurement

- · A.C. PSRR Worse Than D.C. PSRR

- A.C. PSRR Degrades With Frequency

29

Digital circuitry typically causes a lot of noise on digital power lines. If the power source used for analog and/or mixed-signal devices is the same power source that is used for digital components, this noise can couple into the analog and mixed-signal components through their supply pins. To the extent that the analog or mixed-signal components exhibit good power supply rejection, this will not affect the analog or mixed-signal component. However, Power Supply Rejection Ratio (PSRR) as expressed on data sheets usually refers to the difference in a single parameter (e.g., Offset Voltage) with two different stable d.c. supply voltages. This says very little about how well high frequency noise on the supply source is rejected by the component.

Noise rejection on the power supply is never quite as good as the d.c. PSRR described above and gets worse with increasing frequency.

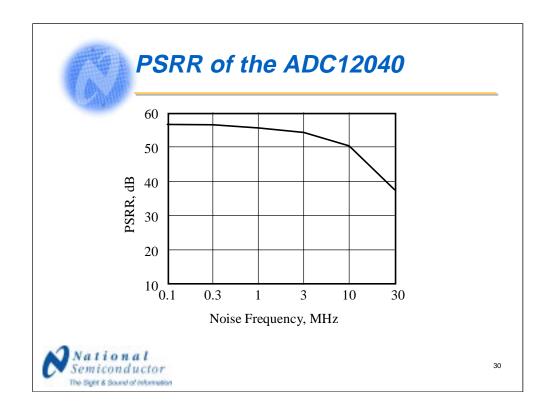

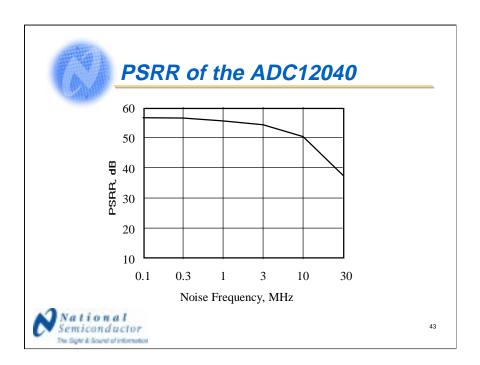

The PSRR of the ADC12040 is excellent, yet PSRR does degrade with higher frequencies. To degrade just 8dB from 100kHz to 10MHz, however, is exceptionally good for any ADC.

This test was performed by providing a 1.2 MHz input frequency to the ADC and a.c. coupling the a constant amplitude (500 mV<sub>P-P</sub>), variable frequency sine wave to the ADC power supply pins. This amplitude was measured right at the supply pins. The ADC reference was 2.0V, so if the PSRR were zero the output amplitude would have been 20\*log(0.5/2.0) = -12.04 dBFS. The supply "noise" frequency amplitude was measured in dB. The PSRR was calculated to be the difference between this output level and 12 dB. So, for example, with 500 mV<sub>P-P</sub> at 10 MHz on the supply pins, I found that the 10MHz frequency bin was at -62 dBFS, so determined PSRR to be

$$-PSRR = -62 - (-12) = -62 + 12 = -50 dB$$

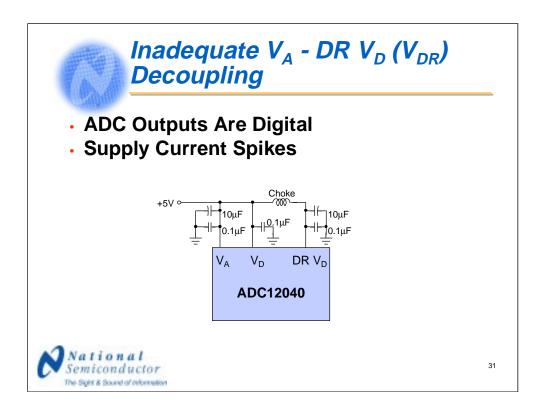

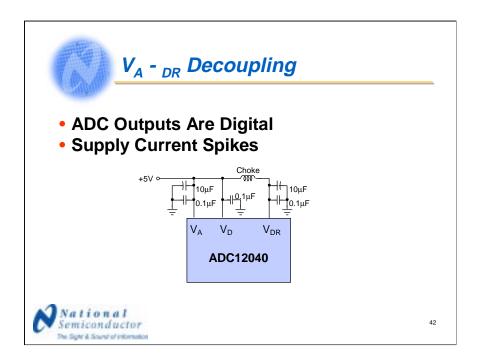

The digital output drivers of the ADC provide fairly fast edge rates (rise and fall times). This causes the output drivers to draw varying amounts of dynamic supply current with fast rise times to charge whatever capacitance is on the outputs when the output data must go from a logic low to a logic high. The noise thus introduced on the output driver supply can upset any analog circuitry if it is not decoupled from the ADC output drivers.

Shown here is a very good power supply decoupling technique.

### **Noisy Components/Circuitry**

- ADC Input Signal Conditioning is Common

- Noisy Amplifiers

- Resistors

- Noise

- Use Low Values

- High Frequency Coupling

- Resistor Packs

- Bandpass Characteristics

- Oscillation

- D.C. Offset

32

There is almost always a need for some signal conditioning between the stimulus source and the ADC, giving rise to a few opportunities to get noise injected into the system and to create signal distortion.

Amplifier noise is an obvious source of noise, but the fact is that it is extremely difficult to find an amplifier with a noise performance that will not degrade the system noise performance below that possible with a high resolution (12-bit or higher) ADC. Be very careful when choosing amplifiers and buffers in your signal conditioning circuitry.

We often think of resistors as noisy devices, but choosing resistor values that are as low as practical can keep noise to a level where system performance is not compromised.

Remember that capacitive coupling of high frequency energy around some components and into unwanted areas can be a problem, so be careful with PCB (printed circuit board) layout.

Resistor packs can be good for minimizing the number of components mounted or inserted and for good matching. However, the small package means there are fairly large capacitances between the individual resistors, leading to the possibility of high frequency coupling when we do not want it. Resistor packs in the input/feedback areas of an op-amp, for example, might cause a change in bandpass characteristics or encourage high frequency oscillations. Sometimes a high frequency oscillation show up as a d.c. offset.

The fact that the input signal is *quantized* means that noise is added to it. Quantization noise is less with higher resolution as the input range is divided into a greater number of smaller ranges.

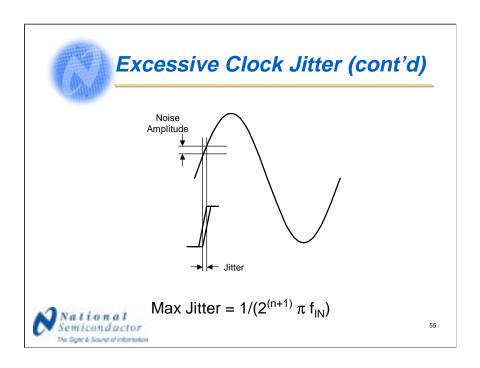

#### Clock Noise

- Clock Can Add Noise

- Clock Can Be Noisy, Exhibiting Jitter

- For Ideal SNR, Max Jitter =  $1/(2^{(n+1)} \pi f_{IN})$

- Transmission Line

- Clock Line Longer Than t<sub>r</sub> / (6 \* Delay)

Should Be Terminated

34

The ADC clock signal can add noise to the system if proper care is not taken in its handling. Improper routing of the clock line can cause clock noise to be coupled into the analog signal chain.

A clock signal that has cycle-to-cycle variation in its duty cycle is said to exhibit **jitter**. Clock jitter causes an uncertainty in the precise sampling time, resulting in a reduction of noise performance. Jitter can result from the use of a poor clock source, poor layout and grounding and from energy being coupled into the clock line from other signal sources. Sometimes you will see this formula as Max Jitter =  $(V_{IN\_P-P} / V_{FS})/(2^n \pi f_{IN})$ , which allows one LSB of noise. Changing  $2^n$  to  $2^{(n+1)}$  reduces the allowable noise to ½ LSB and is more conservative. Changing the numerator to "1" gives us the allowable jitter for a full-scale input signal that will not produce noise.

The clock line should be treated as a transmission line when its length exceeds the clock rise time/(6 x Delay), where "Delay" is the propagation rate of the signal on the board, and is about 150ps/inch (6ps/mm) on a board of FR4 material. Since it is a transmission line, the clock line should be properly terminated. Other authors use factors of 3 to 4 in place of the 6 shown here, but these are marginal values. Using (6 \* Delay) is more conservative and allows for variation in the dielectric constant of the board from one manufacturer to another and for layout variations.

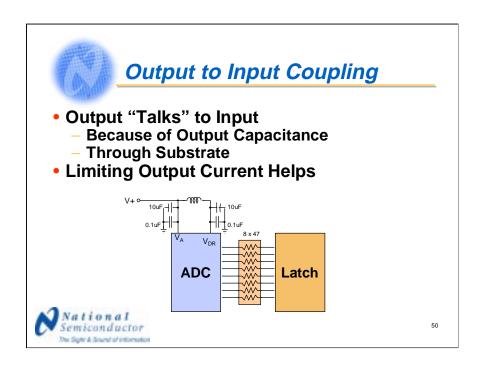

### **Output to Input Coupling**

- Output "Talks" to Input

- Because of Output Capacitance

- Through Substrate

- Limiting Output Current (with Resistors)

Can Help

When the lower output transistor of the output turns on to discharge the capacitance at the ADC outputs, those currents are dumped into the substrate, causing the substrate to rise above the external ground potential, very effectively adding noise to the analog input signal.

Preventing this requires minimization of the output capacitance to minimize the amount of current that is forced into the ADC substrate. To do this it is necessary to drive only a single, low input capacitance pin with each ADC output and to place that input as close as possible to the ADC output pin that is driving it. This means that we must avoid using the ADC outputs to drive a bus. It is also helpful to use 47- to 56-Ohm series resistors at the ADC output pins, located as close to the ADC output pins as possible. This limits the amount of current used to discharge (and charge) the output capacitance.

35

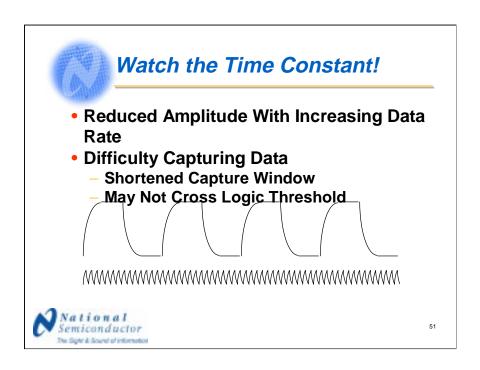

# Watch the Time Constant!

- Reduced Amplitude With Increasing Data Rate

- Difficulty Capturing Data

- Shortened Capture Window

- May Not Cross Logic Threshold

36

The time constant of the series output resistors and the capacitances after those resistors form a time constant that effectively reduces the output amplitude as the output data rate increases. This can make it difficult to capture the output data because the capture window is reduced. As the time constant becomes longer or the output data rate becomes faster we may find that the signal does not even cross the logic threshold and no data is captured at all.

Be careful of this time constant. At very high frequencies it may not be practical to use series resistors at the ADC output. When this is the case, it is absolutely essential to have the driven circuit <u>very</u> close to the ADC output pins and to use a device with a very low input capacitance.

### Common Design Mistakes With ADCs

- High Capacitance on ADC Outputs

- Overdriving Any Input

- Not Terminating the Clock Line

- Inadequate Conditioning Circuitry

- Inadequate Reference Driver

- Excessive Clock Jitter

37

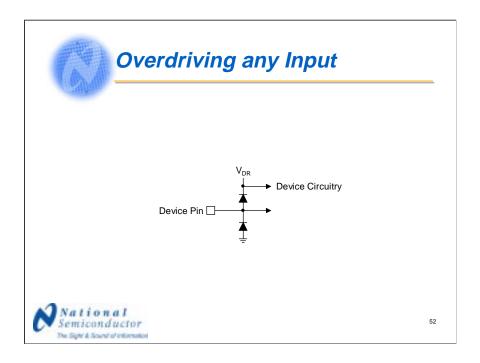

We have discussed or alluded to most of these problems already. However, a word about overdriving any input and about care in driving the reference input is in order.

In addition to the possibility of exceeding the Absolute Maximum Rating of a device, driving any pin beyond the limits of the supply rails is asking for a problem unless the device is designed to handle this condition. Going below ground (or negative supply) can result in a latch-up condition where excessive current is drawn until the device is destroyed. This current will not go away even after the input is returned to its normal operating range, unless the power supply is interrupted. Even when the device does not latch up the device could give erroneous conversions.

Going above the power supply usually results in a lot of distortion. Driving a pin beyond its Absolute Maximum Rating can cause device damage.

- Minimum Sample Rate Limitation

- Using an ADC Below Specified Sample Rate

- Getting Data Below ADC's Minimum Sample Rate

38

Sometimes we can not find an ADC that is specified for the sample rate we need for a system. Usually, an ADC that is operated below its specified rate will operate at least as well at lower sampling rates. However, there are ADCs on the market (none from National Semiconductor) that will not function well if not used very close to their specified sample rate.

Most high speed ADCs have a sample rate below which they do not perform well. The reason for this is that the on-chip capacitors that must hold a charge during the conversion process are very small (to allow for the fast acquisition time required for a high speed ADC). Because they are very small, the charge on them can dissipate if the conversion rate is too slow. Be aware of the minimum sample rate for a converter you are using far below its specified sample rate.

If you need a conversion rate below the minimum acceptable sample rate of a given ADC, simply clock it above its minimum rate and only look at every 2nd, or 3rd or 10th sample.

#### Common Design Mistakes

- Inadequate Attention to Noise Minimization

- Ignoring PSRR

- No Power Decoupling/Bybassing

- Noisy Support Components

- Excessive Clock Jitter

- Treating Clock Line as a Trace

- Inadequate Conditioning Circuitry

- Inadequate Reference Driver

- High Capacitance on ADC Outputs

- Overdriving Any Input

39

There are many possible sources of problems when using high speed ADCs, yet a surprising number of users are not aware of many of them. This leads users to use higher resolution ADCs than really needed as they try to get better noise performance or lower distortion.

In addition to the possibility of exceeding the Absolute Maximum Rating of a device, driving any pin beyond the limits of the supply rails is asking for a problem unless the device is designed to handle this condition. Going below ground (or negative supply) can result in a latchup condition where excessive current is drawn until the device is destroyed. This current will not go away even after the input is returned to its normal operating range, unless the power supply is interrupted. Even when the device does not latch up the device could give erroneous conversions.

Going above the power supply usually results in a lot of distortion. Driving a pin beyond its Absolute Maximum Rating can cause device damage.

- Higher Resolution May Not Be The Answer

- Attention to PSRR and Power Supply Decoupling

- Output to Input Coupling

- Layout and Ground Return Currents

- Clock Jitter

- Clock Line Reflections

40

While using a higher resolution ADC can help improve noise performance, it is not the best solution as even this will fail to give the expected results in a poorly designed circuit. Proper attention to the other things listed here is much more effective than is a higher resolution ADC.

- Noise Can Enter Via The Power Supply

- Specified PSRR Is A D.C. Measurement

- A.C. PSRR Worse Than D.C. PSRR

- A.C. PSRR Degrades With Frequency

41

Digital circuitry typically causes a lot of noise on digital power lines. If the power source used for analog and/or mixed-signal devices is the same power source that is used for digital components, this noise can couple into the analog and mixed-signal components through their supply pins. To the extent that the analog or mixed-signal components exhibit good power supply rejection, this will not affect the analog or mixed-signal component. However, Power Supply Rejection Ratio (PSRR) as expressed on data sheets usually refers to the difference in a single parameter (e.g., Offset Voltage) with two different stable d.c. supply voltages. This says very little about how well high frequency noise on the supply source is rejected by the component.

Noise rejection on the power supply is never quite as good as the d.c. PSRR described above and gets worse with increasing frequency.

The digital output drivers of the ADC provide fairly fast edge rates (rise and fall times). This causes the output drivers to draw varying amounts of dynamic supply current with fast rise times to charge whatever capacitance is on the outputs when the output data must go from a logic low to a logic high. The noise thus introduced on the output driver supply can upset any analog circuitry if it is not decoupled from the ADC output drivers.

Shown here is a very good power supply decoupling technique. The very first thing to do, however, is to minimize the output bus capacitance so less current is required to charge that capacitance.

The PSRR of the ADC12040 is excellent, yet PSRR does degrade with higher frequencies on the supply lines. The 8 dB degradation from 100kHz to 10MHz seen here, however, is exceptionally good for any ADC.

This test was performed by providing a 1.2 MHz input frequency to the ADC and a.c. coupling the a constant amplitude (500 mV<sub>P-P</sub>), variable frequency sine wave to the ADC power supply pins. This amplitude was measured right at the supply pins. The ADC reference was 2.0V, so if the PSRR were zero the output amplitude would have been  $20^*\log(0.5/2.0) = -12.04$  dBFS. The supply "noise" frequency amplitude was measured in dB. The PSRR was calculated to be the difference between this output level and 12 dB. So, for example, with 500 mV<sub>P-P</sub> at 10 MHz on the supply pins, I found that the 10MHz frequency bin was at -62 dBFS, so determined PSRR to be

$$PSRR = -62 - (-12) = -62 + 12 = -50 dB$$

#### Noisy Components/Circuitry

- ADC Input Signal Conditioning is Common

- Noisy Amplifiers

- Resistors

- Noise

- Use Low Values

- High Frequency Coupling

- Resistor Packs

- Bandpass Characteristics

- Oscillation

- D.C. Offset

44

There is almost always a need for some signal conditioning between the stimulus source and the ADC, giving rise to a few opportunities to get noise injected into the system and to create signal distortion.

Amplifier noise is an obvious source of noise, but the fact is that it is extremely difficult to find an amplifier with a noise performance that will not degrade the system noise performance below that possible with a high resolution (12-bit or higher) ADC. Be very careful when choosing amplifiers and buffers in your signal conditioning circuitry.

We often think of resistors as noisy devices, but choosing resistor values that are as low as practical can keep noise to a level where system performance is not compromised.

Remember that capacitive coupling of high frequency energy around some components and into unwanted areas can be a problem, so be careful with PCB (printed circuit board) layout.

Resistor packs can be good for minimizing the number of components mounted or inserted and for good matching. However, the small package means there are fairly large capacitances between the individual resistors, leading to the possibility of high frequency coupling when we do not want it. Resistor packs in the input/feedback areas of an op-amp, for example, might cause a change in bandpass characteristics or encourage high frequency oscillations. Sometimes a high frequency oscillation show up as a d.c. offset.

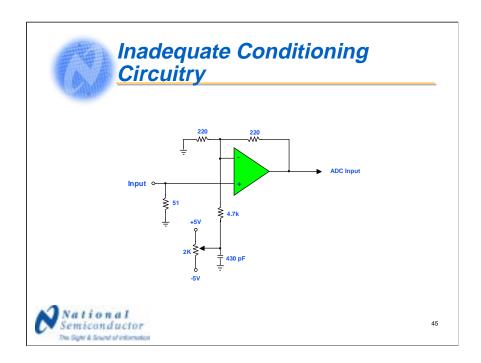

This simple circuit has a nominal gain of +2. The arm of the potentiometer is properly bypassed to prevent the gain from changing with a change of bias setting.

The problems here are two: (1) amplifiers do not like being operated at low gain settings and tend to be a little unstable when forced to do so and (2) the input of most sampling ADCs is a switched capacitor circuit. Such circuits tend to output energy from the input pin and amplifiers do not like to drive such circuits. Both of these conditions lead to ringing, if not oscillation.

The 4.7k-Ohm resistor seems a little on the large side, so you might expect that it will add noise. While this value is larger than we might like to see, it probably is not as much of a problem as the low gain and the driving the switched capacitor input of the ADC.

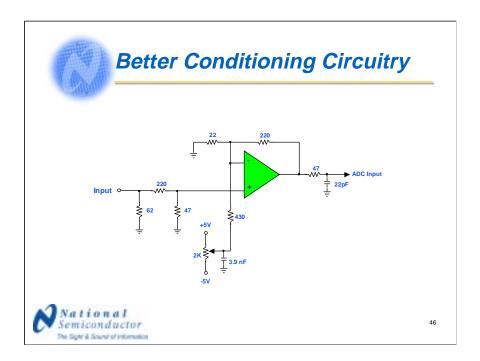

This is a much better solution, The amplifier is operated at a gain of about 11.5 (don't forget the effect of the 430-Ohm resistor on gain!) and the input is padded down so that the overall gain from input to output is about 2. The amplifier is happy with the high gain.

The amplifier is decoupled from the ADC input with a simple RC. The resistor should be large enough for isolation, but small enough to prevent a significant signal loss. Resistors of 20 to 50 Ohms generally work well. The Capacitor is chosen such that the RC cutoff frequency is the ADC sample rate:  $C = 1/(2 * \pi * R * f_s)$ . This will give the best SNR performance. For best distortion performance this RC circuit should be eliminated. For best SINAD, the value of either the resistor or the capacitor should be reduced until SINAD is optimized (-THD = SNR).

- Keep Signal Path Straight

- Do Not Run Analog Lines Parallel to Each Other

- Keep Inductors Well Separated or Orthogonal to Each Other

- Use Care With Resistor Packs

47

Avoiding problems of signal coupling requires careful attention to both capacitive coupling and mutual inductance. Very small capacitances and mutual inductances can be quite effective at coupling high frequency energy.

### Resistor Pack Danger

- \* OPTIONAL RESISTOR NETWORK

\*\* OPTIONAL PULL-UP RESISTOR WHEN USING INTERNAL REFERENCE

48

This innocuous-looking circuit has a hidden danger. The "optional resistor network" has some rather large capacitances that creates problems for even very slow op-amps. For example, the capacitance between the output side of the feedback resistor and the op-amp "+" input side of the two resistors connected there will cause oscillation. Sometimes the frequency of oscillation is so high it is difficult to find and we only see the results of a rectification within the amplifier or the ADC. The result is the production of an offset. If the offset is large enough, the device could be forced into a non-linear mode of operation.

Resistor packs are fine in digital applications, but be careful with them in linear circuits.

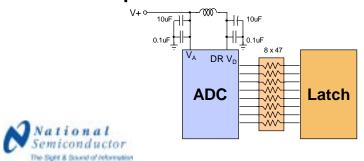

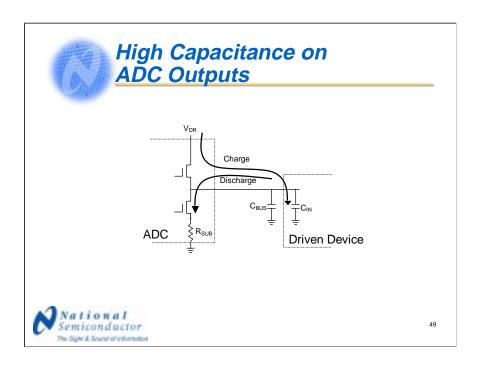

Charging bus and device input capacitances causes noise on the supply line, as we have discussed. Discharging these capacitances adds noise to the ADC substrate, which can appear at the input as noise. The task, then, is to minimize these currents.

Keeping output noise down requires minimization of the output capacitance to minimize the amount of current that is forced into the ADC substrate. To do this it is necessary to drive only a single, low input capacitance pin with each ADC output and to place that input as close as possible to the ADC output pin that is driving it. This means that we must avoid using the ADC outputs to drive a bus. It is also helpful to use 47- to 56-Ohm series resistors at the ADC output pins, located as close to the ADC output pins as possible. This limits the amount of current used to discharge (and charge) the output capacitance.

The time constant of the series output resistors and the capacitances after those resistors form a time constant that effectively reduces the output amplitude as the output data rate increases. This can make it difficult to capture the output data because the capture window is reduced. As the time constant becomes longer or the output data rate becomes faster we may find that the signal does not even cross the logic threshold and no data is captured at all.

Be careful of this time constant. At very high frequencies it may not be practical to use series resistors at the ADC output. When this is the case, it is absolutely essential to have the driven circuit <u>very</u> close to the ADC output pins and to use a device with a very low input capacitance.

The ESD protection diodes on the die will conduct when the input goes far enough above the supply voltage or far enough below device ground. Never assume that these diodes do not conduct until there is 600mV across them. Some of them conduct enough to be a problem with as little as 50 to 100 mV across them! As the current through these diodes become significant enough for that particular circuit, other parasitic diodes and transistors can be turned on. The result can be as dramatic as turning on a very low impedance path between the supply pin and ground. This is known as CMOS latchup and is destructive to the device.

A more common effect is to charge or discharge nodes within the ADC such that conversion accuracy is lost or the device may not function at all.

NEVER allow the pins of a device to go beyond the supply rails.

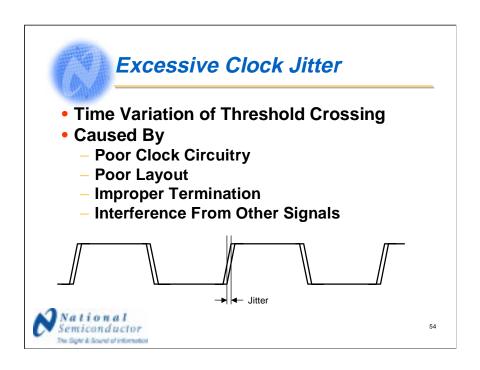

- Clock Can Add Noise to Conversion

- Clock Can Be Noisy, Exhibiting Jitter

- For Ideal SNR,

Max Jitter =  $V_{IN(P_-P)}$  / ( $V_{FS} \times 2^{(n+1)} \times \pi \times f_{IN}$ )

- Transmission Line

- Clock Line Longer Than t<sub>r</sub> / (6 x Delay)

Should Be Terminated

53

The ADC clock signal can add noise to the system if proper care is not taken in its handling. Improper routing of the clock line can cause clock noise to be coupled into the analog signal chain.

A clock signal that has cycle-to-cycle variation in its duty cycle is said to exhibit **jitter**. Clock jitter causes an uncertainty in the precise sampling time, resulting in a reduction of noise performance. Jitter can result from the use of a poor clock source, poor layout and grounding and from energy being coupled into the clock line from other signal sources.

The clock line should be treated as a transmission line when its length exceeds the clock rise time/(6 x Delay), where "Delay" is the propagation rate of the signal on the board, and is about 150ps/inch (6ps/mm) on a board of FR4 material.

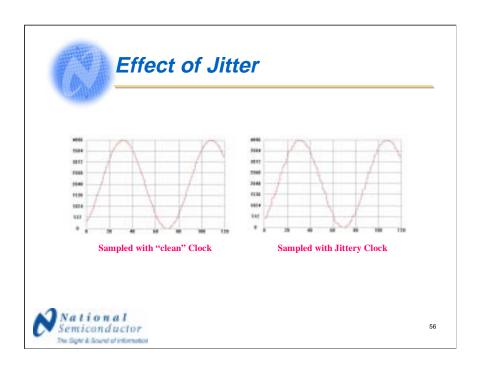

Jitter is the time variation of the threshold/zero crossing of a signal.

Excessive clock jitter will add noise to the conversion result.

As the clock timing changes slightly, there is a change in the exact point of sampling. This causes the ADC to sample a higher or lower point in the signal than it should. The next point could have a different time variation, so a different change from the proper sampling point. The result is a lot of variation in the signal sampling point and noise added to the signal.

These plots from National's WaveVision $^{\text{TM}}$  software show the effects of excessive clock jitter. The noise on the signal is apparent.

- Transmission Line

- Clock Line Longer Than t<sub>r</sub> / (6 \* Delay)

Should Be Terminated

- Unterminated Line Has Reflections and Standing Waves

- Reflections Cause Distortion

- Standing Waves Cause Radiation

57

A line carrying a clock signal on a board of FR-4 material will have a typical delay of 150 ps/inch. With a 2ns rise time, a clock line longer than 2.2 inches must be considered a transmission line to maintain clock signal integrity and to minimize radiation. We suggest that you always treat the clock line as a transmission line and properly terminate it.

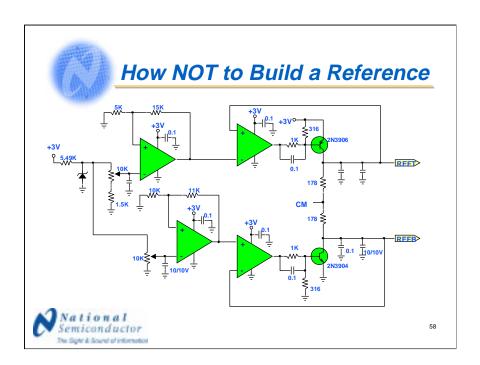

The problem here may not be obvious at first glance, but including the common-emitter gain of a transistor in the feedback loop of an amplifier is a recipe for high frequency oscillation. Also, this circuit has twice as many op-amps as needed and too many different resistor values, which manufacturing people <u>really</u> dislike!

59

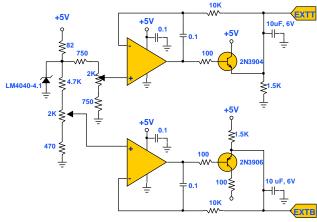

This reference circuit is not only much simpler than the previous one, it is much more stable. One key factor is to choose a slow op-amp. To ensure stability, high frequency gain is killed with a 0.1uF capacitor in each op-amp feedback loop. The transistors are emitter followers, providing current gain, but no voltage gain, which could cause oscillation.

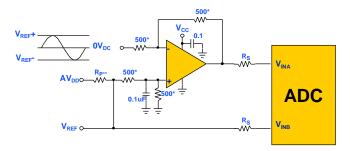

The reference circuit of many ADCs have switches connected to a resistive or capacitive ladder. These switches cause external current pulses at the reference pin(s) as they open and close. A reference drive circuit that is not capable of driving such a load and settling fast enough will result in noise on the reference pin(s), resulting in noisy conversions. It is not necessary to eliminate these voltage spikes, but they must settle before the sampling switch opens.

A reference drive circuit that will not provide enough current to drive the ladder will cause an inaccurate reference voltage to be supplied. A reference circuit with inadequate drive will not have enough current capability to hold the reference stable, resulting in noisy conversions, and will usually have a degraded tempco.

The circuit shown here is a good design for use as a reference driver for ADCs like the ADC1175 and ADC1175-50. Just modify the input dividers for other reference voltages for other ADCs. The potentiometers, of course, could be replaced with a fixed divider, but component tolerances must be taken into account to prevent the possibility of the input signal going beyond the resultant valid range for digitization, which would result in output clipping.

## High Speed ADCs From National – 8-Bits

| ADC         | Res<br>(Bits) | Speed<br>(Msps) | Pwr. Cons<br>(mW) | INL<br>(LSB) | DNL<br>(LSB) | SNR<br>(dB) | SINAD<br>(dB) | SFDR<br>(dB) | @ f <sub>IN</sub><br>(MHz) |

|-------------|---------------|-----------------|-------------------|--------------|--------------|-------------|---------------|--------------|----------------------------|

| ADC1173     | 8             | 15              | 36                | ±0.5         | ±0.4         | 48          | 46            | 51           | 7.5                        |

| ADC1175     | 8             | 20              | 60                | ±0.5         | ±0.35        | 47          | 46            | 58           | 4.4                        |

| ADC08351    | 8             | 42              | 40                | ±0.7         | ±0.6         | 45          | 45            | 54           | 4.4                        |

| ADC1175-50  | 8             | 50              | 125               | ±0.8         | ±0.7         | 44          | 44            | 56           | 19.9                       |

| ADC08060    | 8             | 60              | 1.3/Msps          | ±0.5         | ±0.4         | 47          | 47            | 60           | 25                         |

| ADC08L060   | 8             | 60              | 0.65/Msps         | ±0.5         | ±0.25        | 47.4        | 46.1          | 54.5         | 29                         |

| ADC08100    | 8             | 100             | 1.3/Msps          | ±0.5         | ±0.4         | 46.5        | 46            | 63           | 41                         |

| ADC08200    | 8             | 200             | 1.05/Msps         | +1.0<br>-0.3 | ±0.4         | 46          | 46            | 60           | 50                         |

| ADC081000 * | 8             | 1000            | 1.4 W *           | ±0.5 *       | ±0.4 *       | 47 *        | 46 *          | 57 *         | 100                        |

<sup>\*</sup> Expected specifications: product in development

60

National Semiconductor provides an increasing range of high speed ADCs. Most applications can be satisfied with a product we provide.

# High Speed ADCs From National – 8- and 10-bits

| ADC       | Res<br>(Bits) | Speed<br>(Msps) | Pwr. Cons<br>(mW) | INL<br>(LSB) | DNL<br>(LSB) | SNR<br>(dB) | SINAD<br>(dB) | SFDR<br>(dB) | @ f <sub>IN</sub><br>(MHz) |

|-----------|---------------|-----------------|-------------------|--------------|--------------|-------------|---------------|--------------|----------------------------|

| ADC10221  | 10            | 15              | 98                | ±0.45        | ±0.35        | 60          | 59            | 72           | 4.4                        |

| ADC10321  | 10            | 20              | 98                | ±0.45        | ±0.35        | 60          | 59            | 72           | 4.4                        |

| ADC10D020 | 2x20          | Dual 20         | 150               | ±0.65        | ±0.35        | 59          | 59            | 75           | 4.7                        |

| ADC10030  | 10            | 30              | 125               | ±0.45        | ±0.4         | 59          | 58            | 68           | 13.5                       |

| ADC10040  | 10            | 40              | 55.6              | ±0.3         | ±0.3         | 59.6        | 59.4          | 80           | 19                         |

| ADC10D040 | 2x40          | 40              | 267               | ±0.65        | ±0.35        | 60          | 59            | 72           | 10.4                       |

| ADC10065  | 10            | 65              | 68.6              | ±0.3         | ±0.3         | 59.3        | 59            | 80           | 32                         |

| ADC10080  | 10            | 80              | 78.6              | ±0.5         | ±0.25        | 59.2        | 59            | 78.8         | 39                         |

# High Speed ADCs From National 12-bits

| ADC       | Res<br>(Bits) | Speed<br>(Msps) | Pwr. Cons<br>(mW) | INL<br>(LSB) | DNL<br>(LSB) | SNR<br>(dB) | SINAD<br>(dB) | SFDR<br>(dB) | @ † <sub>IN</sub><br>(MHz) |

|-----------|---------------|-----------------|-------------------|--------------|--------------|-------------|---------------|--------------|----------------------------|

| ADC12062  | 12            | 1               | 75                | ±0.4         | ±0.4         | 72          | 71            | -            | 0.1                        |

| ADC12662  | 12            | 1.5             | 200               | ±0.4         | ±0.4         | 70          | 69.7          | -            | 0.1                        |

| ADC12081  | 12            | 5               | 105               | ±0.6         | ±0.35        | 68          | 67.6          | 79           | 2.5                        |

| ADC12181  | 12            | 10              | 235               | ±0.7         | ±0.4         | 65          | 64.5          | 73           | 5                          |

| ADC12191  | 12            | 10              | 235               | ±0.7         | ±0.4         | 63          | 62            | 71           | 5                          |

| ADC12281  | 12            | 20              | 443               | ±1.0         | ±0.35        | 65.5        | 65            | 75           | 4.4                        |

| ADC12010  | 12            | 10              | 160               | ±0.5         | ±0.3         | 70          | 69            | 83           | 10                         |

| ADC12020  | 12            | 20              | 185               | ±0.55        | ±0.4         | 70          | 69            | 85           | 10                         |

| ADC12040  | 12            | 40              | 340               | ±0.7         | ±0.4         | 69.5        | 69            | 84           | 10                         |

| ADC12D040 | 2 x 12        | 40              | 600               | ±0.7         | ±0.4         | 68          | 68            | 80           | 10                         |

| ADC12L063 | 12            | 62              | 354               | ±1.0         | ±0.5         | 66          | 65            | 78           | 10                         |

| ADC12L066 | 12            | 66              | 357               | ±1.2         | ±0.4         | 65          | 64            | 73           | 25                         |

| CLC5957   | 12            | 70              | 640               | ±1.5         | ±0.65        | 66          | -             | 74           | 25                         |

Coming: ADC12QS060, ADC12DL040, ADC12L065, ADC12L080

### High Speed ADCs From National – greater than 12-bits

| ADC      | Res<br>(Bits) | Speed<br>(Msps) | Pwr. Cons<br>(mW) | INL<br>(LSB) | DNL<br>(LSB) | SNR<br>(dB) | SINAD<br>(dB) | SFDR<br>(dB) | @ f <sub>IN</sub><br>(MHz) |

|----------|---------------|-----------------|-------------------|--------------|--------------|-------------|---------------|--------------|----------------------------|

| ADC14061 | 14            | 2.5             | 390               | ±0.75        | ±0.33        | 80          | 79            | 90           | 0.5                        |

| ADC14161 | 14            | 2.5             | 390               | ±0.75        | ±0.3         | 80          | 79            | 90           | 0.5                        |

| ADC14071 | 14            | 7.5             | 380               | ±2.2         | ±0.6         | 77          | 74            | 81           | 3.5                        |

| CLC5958  | 14            | 52              | 1,400             | ±1.5         | ±0.3         | 69          | 69            | 80           | 10                         |

| ADC16061 | 16            | 2.5             | 390               | ±3.0         | ±1.0         | 80          | 79            | 91           | 0.5                        |

Coming: ADC14040, ADC1465, ADC14080

## **General Purpose ADCs From National**

| ADC      | Res<br>(Bits) | Speed<br>(ksps) | Pwr. Cons<br>(mW) | INL<br>(LSB) | DNL<br>(LSB) | SNR<br>(dB) | SINAD<br>(dB) | SFDR<br>(dB) | @ f <sub>IN</sub><br>(KHz) |

|----------|---------------|-----------------|-------------------|--------------|--------------|-------------|---------------|--------------|----------------------------|

| ADCS7476 | 16            | 1,000           | 10                | ±0.4         | ±0.5         | 72.5        | 72            | 82           | 100                        |

| ADCS7477 | 10            | 1,000           | 10                | ±0.2         | ±0.3         | 62          | 61.7          | 78           | 100                        |

| ADCS7476 | 8             | 1,000           | 10                | ±0.05        | ±0.07        | 49.7        | 49.7          | 69           | 100                        |

| ADC78H89 | 12            | 500             | 0.5               | ±1           | ±1           | 72.8        | 72.6          | 88           | 100                        |

Coming: ADC78H90 – 8-Channel version of ADC78H89 (same specs) Watch for more . . .

### Summary - ABCs of ADCs

- The ADC

- Review of Definitions

- Sources of Distortion and Noise

- Common Design Mistakes

- ADCs from National Semiconductor

65

We have discussed the Analog-to-Digital Converter and its specifications. We talked about problem sources and how to get around them and ended up with a summary of National Semiconductor's high speed ADC offering.

#### **ADC Web Site**

- Site: www.national.com/appinfo/adc shortcut: www.national.com/adc

- shorter cut: www.nsc.com/adc

- **Link to Selection Guides**

- General Purpose/Industrial

- **High Speed**

- Reference Material

- **Application Notes**

- Articles

- **Evaluation Board Material**

- Eval Board Descriptions

- Manuals

- WaveVision™ Software Download

- **Competitive Cross Reference**

Absolute Maximum Ratings – Voltages and currents beyond which a device may not be stressed without danger of damaging or destroying the device. The device is NOT guaranteed to work when stressed at or near its absolute maximum ratings..

A/D - See ADC.

A/D Converter - See ADC.

A.C. Termination - Transmission line termination technique where a series RC is used at the receiving end of a transmission line.

A.C. Termination – Transmission line termination technique where a series RC is used at the receiving end of a transmission line.

ADC - Analog-to-Digital Converter. A device or circuit used to convert analog information to digital words.

ADC10D040 - A 10-bit, 40 Msps (Megasample per second) ADC

ADC12040 - A 12-bit, 40 Msps (Megasample per second) ADC

ADC14080 - A 14-bit, 80 Msps (Megasample per second) ADC

Aliasing – Conversion of an input frequency to another frequency as a result of the conversion process. The output frequency of an ADC can never exceed ½ the sampling frequency of the ADC without this aliasing. When the input frequency does exceed ½ the sampling frequency, the output frequency becomes the absolute value of [INT( $f_{IN}/f_S + 0.5$ ) \*  $f_S - f_{IN}$ ].

Characteristic Impedance - The impedance a transmission line such that, when driven by a circuit with that output impedance, the line appears to be of infinite length such that it will have no standing waves, no reflections from the end and a constant ratio of voltage to current at a given frequency at every point on the line.

DAC - Digital-to-Analog Converter. A device or circuit used to convert digital words into analog voltages or currents.

Director – The shorter elements of a "Yagi" antenna that directs energy toward the driven element.

DLE - Differential Linearity Error. Same as DNL.

DNL - Differential Non-Linearity. The measure of the maximum deviation from the ideal step size of 1.00 LSB.

ENOB – Effective Number Of Bits. A specification that helps to quantify dynamic performance. ENOB says that the converter performs as if it were a theoretically perfect converter with a resolution of ENOB. That is, an ENOB of 7.4 says that the converter performs, as far as SINAD is concerned, as if it were a perfectly ideal ADC with a resolution of 7.4 bits (assuming you could have fractional bits). The idea behind ENOB comes from the fact that the absolutely perfect ADC has an SNR that comes only from quantization noise and has absolutely no distortion. When this is the case, SINAD is then equal to SNR. Since SNR of the absolutely perfect ADC is SNR = 6.02 \* n +1.76, where "n" is the number of ADC output data bits, SINAD = SNR for a perfect converter, so SINAD = 6.02 \* n + 1.76 and n = (SINAD – 1.76) / 6.02 and we say that ENOB = (SINAD – 1.76) / 6.02.

FFT – Fast Fourier Transform. The FFT is a mathematical operation that converts signals between the time and frequency domains. We generally call the frequency domain (amplitude vs.. frequency) plot an FFT.

EMI/RFI – Electromagnetic Interference/Radio Frequency Interference. This is the radiation of EM (electromagnetic) energy that may interfere with other circuits and systems.

FR-4 – A glass epoxy printed circuit board material of woven glass cloth construction laminate with an epoxy resin binder.

Full-Scale Input Swing – The difference between the maximum and minimum input voltages that will produce a valid ADC output without going over- or under-range.

Gain Error - The error in the slope of the ADC transfer characteristic. It is the difference in the actual and ideal full scale input range values.

IMD – Intermodulation Distortion. This is the creation of new spectral components that result from two or more input frequencies modulating each other when the circuit is nonlinear.

ILE - Integral Linearity Error. This is the same as INL.

INL – Integral Non-Linearity. The maximum departure of the ADC transfer curve from the ideal transfer curve. INL is a measure of how straight is the transfer function curve. There are two popular methods of measuring INL: End Point and Best Fit. The End-Point method is the most conservative, while the Best Fit method gives lower (better-looking) values. National uses the End Point method.

Input Dynamic Range - For an ADC, the range of voltages that can be applied to the input without going under or over range.

Input Offset – The difference between the input value of 1.0 LSB and the input voltage that causes the ADC output code to transition from zero to the first code.

Input Offset Error – The difference between the ideal input value of 0.5 LSB and the input voltage that causes the ADC output code to transition from zero to the first code.

Jitter - The variation in the timing of a signal's rising or falling edge. It can be specified as cycle-to-cycle or long term.

Loop Area – The area between the conductors of outgoing and return currents.

LSB - Least Significant Bit. The bit that has the least weight.

Missing Codes - Those ADC codes that never appear at the ADC output. These codes can not be obtained with any input value.

Nyquist Kate - I ne minimum sampling rate (or frequency) needed to prevent frequency aliasing.

Nyquist Frequency –The maximum input frequency beyond which frequency aliasing results.

Offset Error - This is the same as Input Offset Error.

PC Board - Printed Circuit Board.

PCB - Printed Circuit Board.

Proximity Effect - The phenomenon whereby outgoing and return currents want to flow close to each other.

PSRR – Power Supply Rejection Ratio. A measure of how well a circuit rejects a signal on its power supply. There are two ways to specify PSRR, the most common of which is to specify the change in one parameter when the d.c. value of the power supply is changed. That is, one value of d.c. voltage is applied to the supply pins and the selected parameter (e.g. offset error) is measured. Then another d.c. voltage is applied to the supply pins and the same parameter is again measured. The extent to which the selected parameter does not change when the supply voltage is changed is the d.c. PSRR. This tells us nothing about how well an a.c. signal, such as noise, on the supply line will be rejected by the device.

The other method is the specify how an a.c. signal on the power supply will affect the output of the device. National specifies both methods for most of our ADCs. This provides the all-important a.c. PSRR, but also provides d.c. PSRR that may be compared with competition. Note, however, that the two readings have no relationship to each other.

Quantization – The process of dividing a range of analog voltages or currents into smaller "quanta" (smaller range of voltages or currents) such that each quanta is represented by a single digital code.

Quantization Error – The error introduced as a result of the quantization process. The amount of this error is a function of the resolution of the quantizer. By definition, the quantization error of an ADC is ½ LSB.

Quantization Noise – The noise at the ADC output that is caused by the quantization process. It is defined as 20 \* log (2<sup>(n-1)</sup> \* sqrt(6)), or about 6.02 \* n + 1.76 dB, where "n" is the number of output bits of the ADC.

Quantizer - A circuit that carries out the quantization process. Another name for an Analog-to-Digital Converter.

Reference Voltage – For an ADC, the reference voltage is the voltage against which the analog input or an ADC is compared to determine the ADC output code. For a DAC, the reference voltage is multiplied with the ratio of the DAC input code to its (full-scale code + 1) to determine its analog output.

Reflector – The longer elements of a "Yagi" antenna that reflect energy back to the driven element.

Resolution – A measure of how well the ADC input is "resolved", or how well the value of an LSB represents the analog input. Resolution is usually expressed in bits, and then indicates the number of bits available in the ADC output word.

The number of discrete output states or values of an ADC or a DAC, Can also be expressed in the number of digital bits in the output (for ADCs) or the input (for DACs).

Sampling Noise – The inherent noise of an ADC that comes from the steps in the transfer function.

Scale Factor – The effective multiplier of the analog reference voltage input to an ADC or DAC. This value is usually one, but can be any whole or fractional number.

Series Termination - Adding a resistor in series with a transmission line such that the driver output impedance plus the resistance of this external resistor is equal to the characteristic impedance of the transmission line.

S/(N+D) - Signal-to-Noise Plus Distortion. See SINAD.

SINAD – Signal-to-Noise And Distortion ratio. A combination of the SNR and THD specifications, SINAD is defined as the rms value of the fundamental signal to the rms value of all of the other spectral components below half the clock frequency, including harmonics but excluding d.c. SINAD can be calculated from SNR and THD. Because it compares all undesired frequency components at the output with desired frequency. It is an overall measure of the dynamic performance of the ADC. SINAD is also known as SNDR, S/(N+D) and Signal-to-Noise Plus Distortion.

Skin Effect - The phenomenon by which high frequency current flow is restricted to the surface, or skin, of a conductor.

SNDR – Signal-to-Noise And Distortion Ratio. See SINAD.

SNR – Signal-to-Noise Ratio. The ratio of the power in the signal to the power in all other spectral components below ½ the sampling frequency, excluding harmonics and d.c.

Split Ground Plane - Concept where analog and digital grounds are in a single PCB layer and only connected at a single point.

Substrate – The base semiconductor material upon with solid state devices are built. The substrate is resistive with a resistance that is on the order of a few Ohms.

THD – Total Harmonic Distortion. The ratio of the rms total of a specified number of harmonic components to the rms value of the output signal. National uses the first nine harmonics ( $f_2$  through  $f_{10}$ ).

Through Hole – The hole that goes through a printed circuit board to connect together lines and/or planes in two or more layers

$V_{\mathsf{REF}}$  – See "Reference Voltage".

$Z_{0}$  – The characteristic impedance of a transmission line